Art Swift Delivers Keynote and Speaks on Panel at COOL Chips 24

Event

Date

April 13 – 14, 2021

Venue

Online Event

About Esperanto Technologies:

Esperanto Technologies develops high-performance, energy-efficient computing solutions for Artificial Intelligence / Machine Learning based on the open standard RISC-V instruction set architecture. Esperanto is headquartered in Mountain View, California with engineering sites in Portland, Oregon and Austin, Texas in the United States and multiple sites in Europe. Esperanto has brought together a seasoned team of experienced processor and software engineers with the goal of making RISC-V the architecture of choice for compute-intensive applications such as AI and Machine Learning. For more information, please visit https://www.esperanto.ai/

News Articles

Art Swift, President and CEO of Esperanto Technologies™, will deliver a keynote and also speak on a panel at COOL Chips 24.

- When: April 14 and 15 (Japan time.)

- Where: Virtual event, online.

- Agenda: COOL Chips www.coolchips.org/2021/advance-program/

Keynote: High-Efficiency Inferencing for Scalable Machine Learning

- Speaker: Art Swift (Esperanto Technologies)

- Abstract: The extraordinary market demand for large-scale machine learning solutions requires more than GPUs, FPGAs, or large multiplier arrays. These approaches deliver high performance, but at high costs: high power consumption, prohibitively complicated programming models, and unacceptable inflexibility. Esperanto Technologies CEO Art Swift will describe the architectural approach and design methodology for the company’s first supercomputer-on-chip solution for ML inferencing acceleration. The ET-SoC-1 combines the traditional flexibility and programmability of CPU cores with the high efficiency of autonomous tensor processing to deliver unmatched system-level efficiency and all-layer ML acceleration. Every element of Esperanto’s integrated solution represents best-in-class technology: the simplicity of the RISC-V instruction set, proprietary instruction-set extensions for machine learning, an on-chip mesh interconnect, a uniquely optimized memory hierarchy, state of the art process technology, and custom low-voltage circuits. In this way, Esperanto delivers more performance per watt than existing products without compromising flexibility.

- When: April 15, 2021 (Japan time)

Panel Discussion: “Hot” Techs for “Cool” AI Computing: Do We have Enough Tricks?

- Organizer and Moderator: Masato Motomura (Tokyo Tech)

- Panelists:

Yusuke Doi (Preferred Networks, Japan)

Avi Baum (Hailo, Israel)

Art Swift (Esperanto Technologies, USA)

Mitsuhisa Sato (Riken, Japan) - Abstract: It is often mentioned that data is the new oil in the 21st century. Importantly, oil was able to drive industrial revolution only after the advent of combustion engine. By analogy, data can drive AI revolution only after the right silicon engines, i.e., cool chips. The panel will discuss hot topics regarding this important role that cool chips should fulfill for AI computing from various aspects.

- When: April 14, 2021 (Japan time)

About COOL Chips 24: See www.coolchips.org/2021/

Video: Art Swift @CES 2021! “RISC-V and the Future of Open-Source Computing”

News Articles

Video from CES 2021: “RISC-V and the Future of Open-Source Computing”

Video from CES 2021: “RISC-V and the Future of Open-Source Computing”

- Calista Redmond, CEO, RISC-V International.

- Art Swift, CEO, Esperanto Technologies.

- Krste Asanovic, Chief Architect and Co-Founder, SiFive.

- Ted Marena, Sr. Business Director, RISC-V, Western Digital.

Esperanto Technologies to Reveal Chip with 1000+ Cores at RISC-V Summit

PRESS RELEASE

Dec. 1, 2020

About Esperanto Technologies

Esperanto Technologies develops high-performance, energy-efficient computing solutions for Artificial Intelligence / Machine Learning based on the open standard RISC-V instruction set architecture. Esperanto is headquartered in Mountain View, California with engineering sites in Portland, Oregon and Austin, Texas in the United States and multiple sites in Europe. Esperanto has brought together a seasoned team of experienced processor and software engineers with the goal of making RISC-V the architecture of choice for compute-intensive applications such as AI and Machine Learning. For more information, please visit https://www.esperanto.ai/

About the RISC-V Summit

The third annual RISC-V Summit will highlight the continued rapid expansion of the RISC-V ecosystem, presenting both commercial offerings and exciting open-source developments. Newcomers to RISC-V, as well as the seasoned developers who are interested in broadening their toolsets, are invited to choose from the broad range of tutorials. The comprehensive 100% virtual event will feature keynotes from industry pioneers as well as thought-provoking panel discussions. Network with thought-leaders, technology companies, and researchers spearheading the adoption of this evolutionary change in the silicon market.

All trademarks or registered trademarks are the property of Esperanto Technologies or their respective holders.

News Articles

Art Swift, CEO of Esperanto Technologies, will present chip that accelerates Machine Learning based on RISC-V ISA

MOUNTAIN VIEW, Calif., Dec. 1, 2020 – Esperanto Technologies™, developer of high-performance, energy-efficient computing solutions based on RISC-V for Artificial Intelligence (AI), Machine Learning (ML) and Deep Learning (DL) applications, will participate in the RISC-V Summit, December 8-10, 2020. Art Swift, CEO of Esperanto, will deliver the presentation: Esperanto Accelerates Machine Learning with 1000+ Low-Power RISC-V Cores on a Single Chip on Tuesday, December 8.

- What: RISC-V Summit.

- Where: Virtual event, online.

- When: December 8, 2020.

- Agenda: View the agenda here.

- Register here: https://riscv.informatech.com/2020/registrations/Attendee

Presentation: Esperanto Accelerates Machine Learning With 1000+ Low-Power RISC-V Cores on a Single Chip

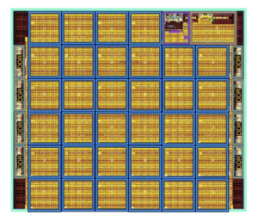

- Esperanto Technologies has developed a ground-breaking accelerator chip for large-scale machine learning applications employing over 1000 RISC-V cores.

- In this talk, Esperanto provides an overview of the company’s new ET-SoC-1 chip, which features two kinds of general-purpose 64-bit RISC-V cores. The ET-Maxion, previewed at the RISC-V Summit in 2018, is a superscalar out-of-order core delivering high performance for modern operating systems and applications. The complementary ET-Minion core designed by Esperanto is a leaner, energy efficient, in-order multithreaded core with a vector/tensor accelerator unit at the heart of the massively parallel compute array.

- The chip’s performance and efficiency is derived from a combination of factors, including the simplicity of the RISC-V instruction set, wide vector/tensor units on every ET-Minion core, a uniquely optimized memory hierarchy, state of the art process technology, and custom pipeline architecture and low-voltage circuits which enables more energy-efficient operation. The result is that Esperanto will deliver better performance per watt than legacy CPU and GPU solutions, as well as competing fixed-function designs without compromising generally purpose flexibility.

2020年11月のRISC-V Day Tokyoでエスペラントの技術をお聞き下さい

PRESS RELEASE

10月30日、2020年

エスペラント技術について

エスペラント・テクノロジーズは、オープンスタンダードのRISC-V命令セット・アーキテクチャをベースに、人工知能/機械学習のための高性能でエネルギー効率の高いコンピューティング・ソリューションを開発しています。エスペラント社はカリフォルニア州マウンテンビューに本社を置き、米国ではオレゴン州ポートランドとテキサス州オースティンにエンジニアリング拠点があり、ヨーロッパにも複数の拠点があります。詳細は https://www.esperanto.ai/をご覧ください。

RISC-V Day Tokyoについて

RISC-V Day Tokyoは日本最大のRISC-Vイベントです。2020年にはCOVID-19の開催により100%オンライン化されます。RISC-Vエコシステムのメンバーが、IoT、AI、セキュリティ、モバイル、ストレージ、ウェアラブル、オートモーティブなどのアプリケーションにまたがる研究、技術、成果、製品を発表し、コラボレーションと技術交流を行います。RISC-Vは、アーキテクチャへの魅力的なライセンスフリーのアプローチとして、急速に支持を集めています。このオープンスタンダードのコラボレーションは、シリコン市場の確立された秩序を変革し、再構築することになるでしょう。 RISC-Vについての詳細は https://riscv.orgをご覧ください。

Esperanto Technologies Press Contacts for Tokyo Event:

Eiji Kasahara, [email protected]

Mike Buchanan, [email protected]

All trademarks or registered trademarks are the property of Esperanto Technologies or their respective holders.

2020年11月のRISC-V Day Tokyoでエスペラントの技術をお聞き下さい

2020年11月のRISC-V Day Tokyoでエスペラントの技術をお聞き下さい

カリフォルニア州マウンテンビュー、10月30日、2020年 –人工知能(AI)、機械学習(ML)、ディープラーニング(DL)アプリケーション向けにRISC-Vベースの高性能でエネルギー効率の高いコンピューティングソリューションを開発しているエスペラント・テクノロジーズ(Esperanto Technologies™)は、2020年11月5-6日に開催される「RISC-V Day Tokyo」の主要スポンサーを務めます。

- 会議: RISC-V Day Tokyo

- 会場: 100% オンライン

- 日程: 2020年11月5日~6日 9:00~18:00 (日本時間)

- アジェンダ: View the agenda here. (http://riscv-association.jp/en/riscv-day-tokyo-2020-en/)

- お申し込み(無料)はこちら: https://peatix.com/event/1666430

エスペラントテクノロジーズのプレゼンテーション: RISC-V機械学習SoCのためのエスペラントの検証手法

- 著者: エスペラント・テクノロジーズ シニア・テクニカル・リードのShankar Jayaratnam氏とエンジニアリング・ディレクターのRaymond Tang氏。

- エスペラントは、大規模な機械学習推論アプリケーションのためのRISC-VベースのSoCを開発しました。各汎用RISC-Vコンピュートコアには、機械学習アルゴリズムを高速化するためのベクトル/テンソル処理ユニットが搭載されています。多くのアクティブ並列スレッドがオンチップのメッシュネットワークを介して通信し、エスペラントの命令セット拡張機能がISA検証に複雑な層を追加しました。オープンソースのRISC-V準拠のテストスイートは、最初の一歩となりました。しかし、非常に低い消費電力と非常に高い性能の要件を満たすためには、シリコンが入手可能になる前に、常に進化し続けるAIソフトウェア・スタックで消費電力と性能を予測することは困難でした。これらの問題を解決するために、エスペラントの統一検証プラットフォームは、複数のベンチソースを維持することなく、異なる階層の設計を検証することを可能にしました。このプラットフォームは、機能検証にシミュレーションとエミュレーションを使用し、AIソフトウェア・スタックを直接実行し、SoC全体をMHzの周波数でエミュレートしました。その結果、重要な機能と性能の問題を早期に発見することができ、ソフトウェア・スタックをより迅速に成熟させることができました。エスペラント独自のカバレッジ手法では、ハードウェアとソフトウェアのコ・シミュレーションと仮想プラットフォームを使用して、マイクロアーキテクチャの痕跡を抽出し、テープアウト品質を実現しました。SoCトポロジ全体のコンパイルとシミュレーションには2時間を要し、デバッグのターンアラウンドを迅速に行うことができました。

RISC-V Day Tokyoに参加して、オープンスタンダードのコラボレーションを通じてマイクロプロセッサIP市場を変革する破壊的な力の一部になり、エスペラント技術についてお聞きください。

Hear Esperanto Technologies at RISC-V Day Tokyo, November 2020

PRESS RELEASE

Oct. 30, 2020

About Esperanto Technologies

Esperanto Technologies develops high-performance, energy-efficient computing solutions for Artificial Intelligence / Machine Learning based on the open standard RISC-V instruction set architecture. Esperanto is headquartered in Mountain View, California with engineering sites in Portland, Oregon and Austin, Texas in the United States and multiple sites in Europe. For more information, please visit https://www.esperanto.ai/

About the RISC-V Day Tokyo

RISC-V Day Tokyo is Japan’s largest RISC-V event. In 2020, it will be 100% online due to COVID-19. RISC-V ecosystem members present their research, technologies, results and products across IoT, AI, security, mobile, storage, wearable, automotive and other applications, for collaboration and technology exchange. RISC-V is fast gaining support as an attractive license-free approach to architecture. This open standard collaboration will transform and reshape the established order of the silicon market. For more about RISC-V, see https://riscv.org.

Esperanto Technologies Press Contacts for Tokyo Event:

Eiji Kasahara, [email protected]

Mike Buchanan, [email protected]

All trademarks or registered trademarks are the property of Esperanto Technologies or their respective holders.

News Articles

Esperanto Technologies Delivers Presentation on RISC-V Machine Learning SoC Verification

MOUNTAIN VIEW, Calif., Oct. 30, 2020 – Esperanto Technologies™, developer of high-performance, energy-efficient computing solutions based on RISC-V for artificial intelligence (AI), machine learning (ML) and Deep Learning (DL) applications, is a leading sponsor for RISC-V Day Tokyo, November 5-6, 2020. Esperanto will also present a technical paper on verification of its RISC-V based SoC on Friday, November 6.

- What: RISC-V Day Tokyo.

- Where: 100% online.

- When: November 5 − 6, 2020, from 9:00 − 18:00 JST (GMT+9).

- Agenda: View the agenda here.

- Register here: https://peatix.com/event/1666430

Esperanto Technologies Presentation: Esperanto’s Verification Methodology for a RISC-V Machine Learning SoC

- Authors: Shankar Jayaratnam, Senior Technical Lead, and Raymond Tang, Engineering Director, at Esperanto Technologies.

- Esperanto has developed a RISC-V-based SoC for large scale machine learning inference applications. Each general purpose RISC-V compute core is equipped with a vector/tensor processing unit to accelerate machine learning algorithms. Many active parallel threads communicate over an on-chip mesh network, and Esperanto’s instruction-set extensions added an extra layer of complexity to ISA verification. The open-source RISC-V compliance test suite was a good first step. Yet, to deliver the extremely low power and very high performance requirements, it was challenging to predict power and performance with a constantly evolving AI software stack prior to silicon availability. To solve these problems, Esperanto’s unified verification platform allowed verifying different hierarchies of design without the need to maintain multiple bench sources. This platform used simulation and emulation for functional verification, running the AI software stack directly, and emulating the full SoC at MHz frequencies. As a result, critical functional and performance issues could be identified earlier, allowing the software stack to mature more quickly. Esperanto’s unique coverage methodology used hardware/software co-simulation and virtual platforms to extract micro-architectural traces and achieve tape-out quality. Compiling and simulating the full SoC topology took as little as 2 hours, for fast debug turnaround.

Attend RISC-V Day Tokyo to be part of the disruptive force transforming the microprocessor IP market through open standard collaboration, and hear about Esperanto technology.

Martin Fink Joins Esperanto Technologies Board of Directors

In The News

March 19th, 2020

News Articles

Technology Veteran Brings Deep Computing Knowledge to Esperanto’s Board of Directors

Technology Veteran Brings Deep Computing Knowledge to Esperanto’s Board of Directors

Esperanto Technologies Inc., developer of high-performance, energy-efficient computing solutions for Artificial Intelligence (AI) and Machine Learning (ML) applications based on the open standard RISC-V instruction set architecture, has appointed Martin Fink to its Board of Directors.

Fink has long been a champion of RISC-V solutions, a member and frequent speaker at the RISC-V Foundation since 2017. He is a respected and valuable player in the ecosystem, to Esperanto’s advantage. RISC-V represents a free and open ISA, enabling a new era of processor innovation through open standard collaboration. Born in academia and research, RISC-V ISA delivers a new level of free, extensible software and hardware freedom on architecture, paving the way for the next 50 years of computing design and innovation.

Fink most recently served as Western Digital Corp. chief technology officer (CTO). Previously, he was CTO and director of HP Labs at Hewlett Packard Enterprise. Fink worked in a wide range of business and technology leadership roles during his 30-year career at HP/HPE. Prior to being named CTO and director of HP Labs at HPE in 2012, he was senior vice president and general manager of Business Critical Systems (BCS) for HP’s Enterprise, Storage and Servers (ESS) business unit. He previously led HP’s Open Source and Linux Organization and the NonStop Enterprise Division. Fink is a graduate of Loyalist College in Ontario, Canada, where he studied electronics engineering and holds an MBA from Colorado State University. He is also a co-inventor on two patents.

“Martin is a respected technologist and a leading voice on the value and promise of RISC-V based designs, and will help accelerate our continued innovation and expansion,” said Art Swift, president and CEO of Esperanto.

Fink joins Dave Ditzel, Chairman and Founder; Art Swift, President and CEO; Geoffrey Baehr of Almaz Capital; and Tong Xie of Decent Capital on the Esperanto Technologies Board of Directors.