See Esperanto Technologies at the RISC-V Summit 2021

Esperanto Delivers Presentations and Exhibits at the RISC-V Summit 2021

Esperanto Technologies™, developer of high-performance, energy-efficient machine learning (ML) inference accelerators based on the RISC-V instruction set, announces its participation in The RISC-V Summit 2021, co-located with the Design Automation Conference and SEMICON West. Esperanto will deliver several presentations, and exhibit at the event.

- Where: Moscone Center West, San Francisco, CA, and online.

- When: December 6-8, 2021

- See: https://events.linuxfoundation.org/riscv-summit/

Highlights:

- Presentation by Art Swift, President and CEO, Esperanto Technologies.

- Technical Presentation: “Esperanto’s Custom RISC-V ISA Extensions for Energy-Efficient Machine Learning Applications” by Darren Jones, VP VLSI Engineering, Esperanto Technologies on Wednesday, December 8, 9:30 – 9:55am.

- Lightning Talk: “Functional Gap between RISC-V V and SPIR-V: a Study Case on the Graphics Domain” by Abel Bernabeu of Esperanto Technologies, Wednesday, December 8, 9:00 – 9:10am.

- Exhibit: Esperanto will feature its energy-efficient AI solutions.

Esperanto is a Gold sponsor of the RISC-V Summit.

About The RISC-V Summit 2021:

RISC-V Summit brings the community together to show the power open collaboration can have on the processor industry. The audience spans across industries, organizations, workloads, and geographies to learn about the technology advancements in the RISC-V ecosystem and visibility of RISC-V successes. See https://events.linuxfoundation.org/riscv-summit/

About Esperanto Technologies:

Esperanto Technologies develops high-performance, energy-efficient computing solutions for Artificial Intelligence / Machine Learning based on the open standard RISC-V instruction set architecture. For more information, please visit https://old.esperanto.ai/

EE Journal: “Esperanto coaxes 1092 RISC-V Processors to Dance on the Head of a Pin, er Chip”

A new article, by Steven Leibson in EE Journal: “Machine Learning: Esperanto coaxes 1092 RISC-V Processors to Dance on the Head of a Pin, er Chip”

Leibson writes:

- Dave Ditzel has a legendary history with computing and microprocessors. He joined AT&T Bell Labs to work on C language development. While there, he developed several generations of processors designed to execute optimized compiled C programs including CRISP, Bell Labs’s “C-language Reduced Instruction Set Processor.”

- Ditzel presented details of Esperanto’s ET-SoC-1 ML (machine learning) inference chip at Hot Chips 33 in August. This chip fully displays Ditzel’s long, long association with RISC processors. The ET-SoC-1 ML inference engine incorporates 1092 (that’s “one thousand ninety-two”) customized, 64-bit RISC-V microprocessor cores, 160 Mbytes of on-chip SRAM, and assorted I/O ports – all on one 7nm die.

- “Ambitious” is an understated word for this chip design.

See Esperanto at RISC-V Days Tokyo 2021

PRESS RELEASE

October 9th, 2021

About RISC-V Days Tokyo 2021:

This event is in collaboration with JASA (Embedded Systems Technology Association), the ET & IoT 2021 Exhibition, RISC-V International (https://riscv.org), and Khronos Group (https://jp.khronos.org). See https://riscv-days-tokyo-2021-utumn.peatix.com/event/3020158/

Date

November 17-19, 2021

Location

Beverly hills

Venue

Pacifico Yokohama Hotel, and online

About Esperanto Technologies:

Esperanto Technologies develops high-performance, energy-efficient computing solutions for Artificial Intelligence / Machine Learning based on the open standard RISC-V instruction set architecture. For more information, please visit https://www.esperanto.ai/

News Articles

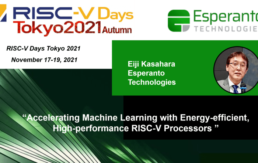

Esperanto Technologies Delivers Presentation at RISC-V Days Tokyo 2021

MOUNTAIN VIEW, Calif., October 11, 2021

Esperanto Technologies™, developer of high-performance, energy-efficient machine learning (ML) inference accelerators based on the RISC-V instruction set, announces its participation in RISC-V Days Tokyo 2021. Esperanto will deliver a presentation at the event.

- Where: Pacifico Yokohama Hotel, and online. Co-located with the ET & IoT 2021 Exhibition (https://www.jasa.or.jp/expo/english/).

- When: November 17-19, 2021, 9: 30-15: 30 JST (Japan Standard Time)

- Presentation: “Accelerating Machine Learning with Energy-efficient, high-performance RISC-V Processors”

- Speaker: Eiji Kasahara of Esperanto Technologies, and BOD member, RISC-V Alliance Japan

- Abstract: What is important for machine learning applications? Energy efficiency, excellent performance, full programmability, and adaptability as algorithms change. Esperanto Technologies solves these challenges with an innovative architecture, leveraging the RISC-V instruction set, and low-power design techniques. Esperanto has developed accelerator chips, and boards, for large scale machine learning inference applications. The SoC uses over 1000 general-purpose RISC-V cores, each equipped with a vector/tensor unit optimized for common machine learning algorithms and data types. Esperanto’s chip, and boards, preserve many benefits of general-purpose programming while simultaneously delivering excellent performance and energy efficiency.

RISC-V Days Tokyo is Japan’s largest RISC-V event, with live and online presentations, exhibition booths, and press conferences. RISC-V Days Tokyo brings together RISC-V-related technology, research, products, and expert engineers, promoting collaboration, technology exchange and business opportunities. Tokyo Day 2020 was held online with 1,053 participants from 11 countries.

The book “Chisel” (Digital Design with Chisel), by Martin Sobert, will be distributed in limited quantities at the venue. A PDF version will also be released.

Esperanto is a Platinum sponsor of RISC-V Days Tokyo 2021.

The Next Platform: RISC-V Upstart Targets ML Inference Performance, Power Efficiency

Startups and tech giants race to build accelerators so artificial intelligence can tackle the complexity of the

real world. A new article, by Jeffrey Burt, in The Next Platform, discussed how Esperanto Technologies.

In EE Times: New Podcast, by Sally Ward-Foxton, with Dave Ditzel

Hear the new EE Times podcast, by Sally Ward-Foxton, with Dave Ditzel: “Data Center Hot Chips, Plus Aart de Geus on AI in Chip Design.”

In Counterpoint: RISC-V to Shake up $8.6-Billion Semiconductor IP Market

In Counterpoint Technology Market Research, by William Li, “RISC-V to Shake up $8.6-Billion Semiconductor IP